Didattica → Sistemi e Reti → Le Memorie

Le memorie hanno il compito di memorizzare dati e programmi (insiemi di istruzioni).

Possiamo immaginarle come grandi contenitori composti di celle in cui in ognuna di esse è conservato 1 bit.

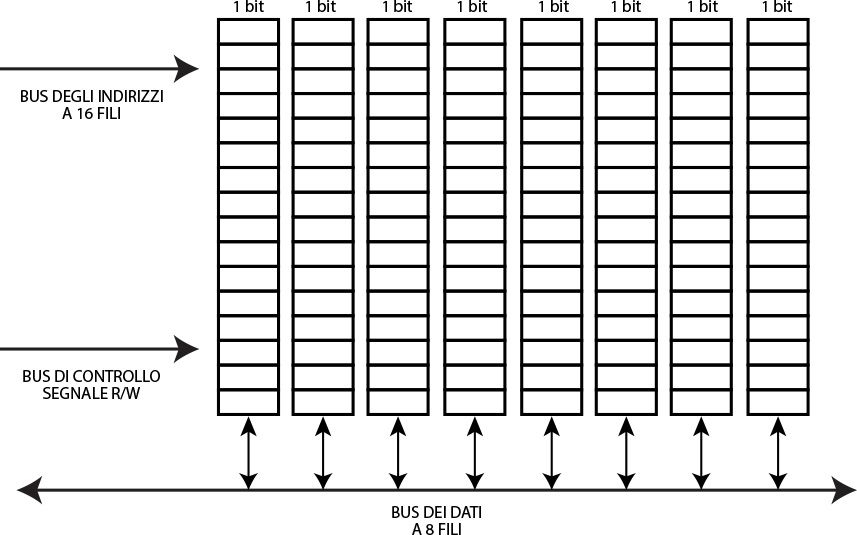

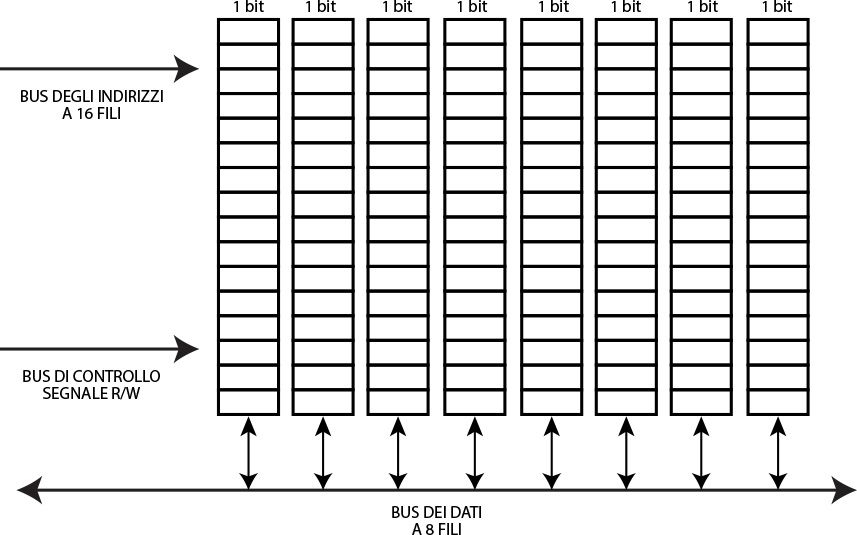

Lo schema di funzionamento di base per la lettura/scrittura di 1 bit sulla o dalla memoria prevede la presenza di tre tipi di bus. Un bus per gli indirizzi che ci permette di individuare la cella (o le celle) in cui andare a leggere/scrivere il dato, un bus di controllo che permette di decidere il tipo di operazione (lettura o scrittura) e un bus dei dati attraverso cui viaggiano bit che vanno letti o memorizzati.

Il bus degli inidirizzi è formato in genere da n fili dove ogni filo può trasportare un bit. In questo modo noi possiamo ottenere 2n indirizzamenti.

Ad esempio se n = 3, allora potremo indirizzare un numero massimo di 8 celle (000, 001, 010, 011,100, 110, 111).

Naturalmente possiamo arricchire la memoria associando ad ogni indirizzo un numero maggiore di bit memorizzati singolarmente in celle disposte su righe. Ad esempio immaginiamo di poter memorizzare ad ogni indirizzo una parola di 8 bit (quindi 8 celle).

In questo caso abbiamo un bus degli indirizzi sempre composto da n fili, un bus di controllo su cui viaggia il segnale R/W che ci indica il tipo di operazione (read, write) e un bus dei dati composto da 8 fili per contenere l’intera parola.

Fig. 1 - Memoria con parallelismo ad 8 bit ed indirizzamento a 16 bit

Un computer contiene tipicamente diversi tipi di memoria: RAM, ROM, cache e memorie di massa.

La caratteristica della RAM è che i dati in essa salvati sono volatili cioè vengono completamente rimossi allo spegnimento del computer. La RAM, per questo motivo, ha bisogno di essere continuamente alimentata per poter essere i suoi dati disponibili. Le memorie RAM si dividono in RAM dinamiche e RAM statiche.

Una memoria dinamica possiamo immaginarla come una matrice composta da una coppia di inidici (i,j) righe e colonne.

Ogni riga individua l’indirizzo della parola in memoria mentre la colonna individua la cella in cui il singolo bit della parola è salvato.

L’indirizzo che viaggia sul bus degli indirizzi, quindi, è composto da due parti: la prima parte che individua le righe e la seconda parte che individua le colonne.

Lo schema di indirizzamento è arricchito da due componenti: il decodificatore di riga che permette di risolvere l’indirizzamento della riga generando il segnale RAS (Row Address Strobe) e il decodificatore di colonna che permette di indirizzare invece le singole celle su ogni riga generando, a partire dalla seconda parte dell’indirizzo in bit, il segnale CAS (Column Address Strobe).

Ogni cella di ogni riga è collegata ad un circuito sense/write tramite 2 line di bit. Una linea collega la cella al bus dei dati e un’altra collega la cella al decodificatore di colonna.

La particolarità di questa memoria a matrice, è l'indirizzamento della memoria varrà la metà della dimensione del bus degli indirizzi (essendo l'indirizzo composto da due parti, una per l'individuazione delle righe e una delle colonne).

La caratteristica di queste RAM è che è necessario, periodicamente (ogni 2,16 ns), una operazione di rinfresco (refresh) del dato affinchè esso possa durare nel tempo.

Questo rallenta i tempi di accesso in quanto durante il refresh, non è possibile effettuare operazioni sulla memoria.

Pensare di eseguire il rinfresco su ogni cella, rende l’operazione troppo onerosa in termini di tempo.

E’ quindi preferibile effettuare il rinfresco una riga alla volta. Per questo si utilizza un buffer di supporto dove spostare il dato ogni volta prima di risalvarlo nella posizione in memoria occupata originariamente.

Anche in questo caso esistono due scelte implementative:

Esistono diverse varianti di DRAM:

Esistono differenti tipi di ROM:

Le memorie cache sono collocate infatti sul chip del microprocessore e sono ad esso collegate attraverso bus di indirizzi e bus di dati privati.

L’introduzione della memoria cache è dovuta al fatto che durante le elaborazioni del microprocessore, capita spesso che dati prelevati dalla memoria RAM vengano utilizzati più di una volta dal microprocessore (località spaziale). Ad esempio le istruzioni di un programma sono eseguite in maniera sequenziale (sono rari i salti). Questo vuol dire che la probabilità che all’istruzione posta all’indirizzo i segue quella all’indirizzo i + di (con di molto piccolo), è molto alta. Inoltre in base al principio di località temporale, se una istruzione viene eseguita al tempo t con alta probabilità la stessa istruzione sarà rieseguita al tempo t + dt (con dt molto più piccolo di t). Con questo si fa riferimento ai cicli.

Ripetere letture sulla RAM più volte, può causare rallentamenti al microprocessore.

La memoria cache, essendo più veloce della RAM, viene utilizzata quindi per immagazzinare dati dalla RAM che vengono utilizzati più spesso dal microprocessore.

La memoria cache è più veloce della RAM per le seguenti ragioni

Le cache sono memorie SRAM che come detto sono anche le più veloci disponibili attualmente.

Quando un microprocessore cerca un dato, effettua un tentativo di accesso alla memoria. Quando questo tentative ha successo, chiameremo questo tentative Hit. Diversamente sarà un Miss che determinerà la ricerca del dato ad un altro livello della memoria fino ad arrivare alla memoria RAM da cui il dato viene preso e memorizzato nella cache da cui poi l’esecuzione del microprocessore riprende.

Esistono però dei problem che una cache deve risolvere:

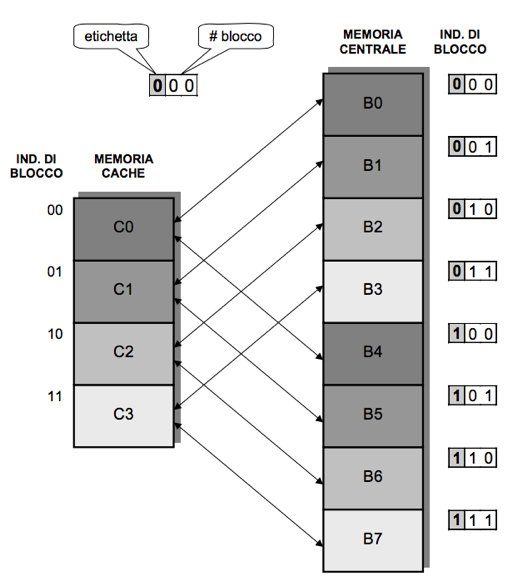

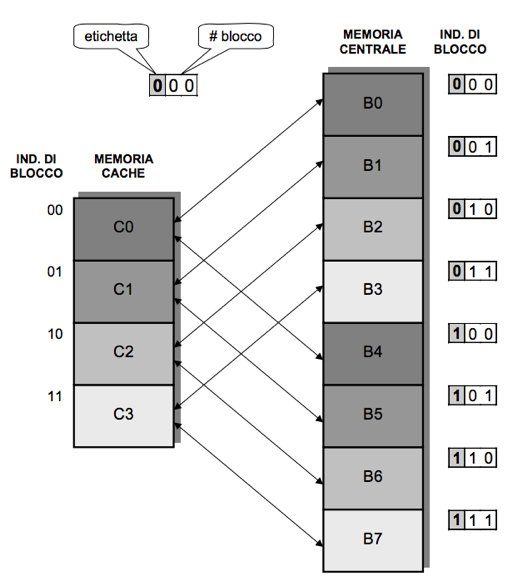

Il metodo di indirizzamento diretto, prevede che in ogni blocco della cache possono essere inseriti un certo numero di blocchi della memoria ram. Ad esempio nel blocco j della cache, si possono memorizzare i blocchi j MOD #blocchi_cache della memoria ram.

Fig. 3 - Indirizzamento diretto

L’idea di indirizzamento è la seguente: gli indirizzi in memoria centrale sono composti da tre parti, una etichetta che identifica un macroblocco della memoria centrale, il #blocco e la parola del blocco a cui si è interessati. Ad esempio l’indirizzo 101 (che è la parte più significativa della parola), identifica il macroblocco B e il blocco 5. Quindi B5. Questo metodo offre: alta velocità, basso costo ma numerosi conflitti di allocazione. Infatti se devo accedere a informazioni nel blocco B0 e B4 ho continui conflitti nonostante la cache sia parzialmente vuota. L’esecuzone dell’indirizzamento diretto segue questi passi:

Se invece sono diversi, allora è necessario caricare il blocco contenente la parola desiderata dalla memoria centrale.

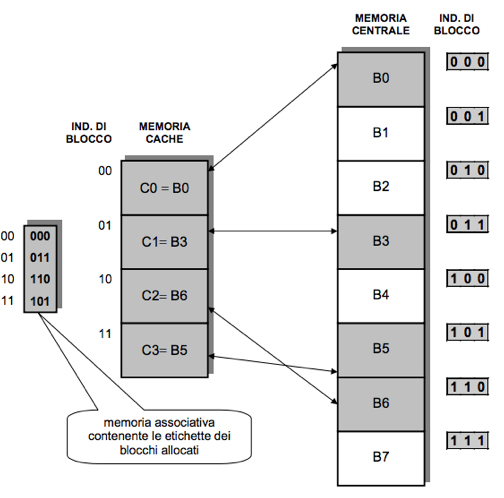

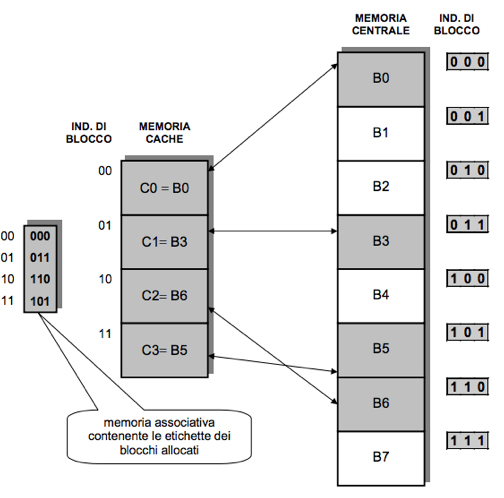

Il metodo associativo, invece, prevede che ogni blocco della memoria centrale possa essere caricato in un qualsiasi blocco della cache. In questo modo si hanno pochi conflitti e si reduce al minimo la presenza di blocchi liberi non utilizzati nella cache. L’unico svantaggio è il costo elevato.

Questo metodo prevede una memoria associativa dove vengono memorizzate le associazioni tra le etichette dei blocchi in memoria centrale e gli indirizzi dei blocchi in cache.

Fig. 4 - Metodo associativo

L’indirizzo della memoria centrale è composto da due parti: l’etichetta che identifica il blocco e la parola che identifica quale parola all’interno del blocco. L’esecuzione è la seguente:

Tuttavia con questo metodo viene usato lo spazio in maniera più efficiente riducendo i miss.

Analizziamo ora il problema della coerenza (cache hit e metodi di scrittura).

Quello che può succedere è che il blocco è in cache ma scrivendo la parola solo in cache la memoria centrale non è più allineata.

Per superare questo problema di coerenza, si usano due politiche differenti di scrittura della parola:

Le Memorie

Le memorie hanno il compito di memorizzare dati e programmi (insiemi di istruzioni).

Possiamo immaginarle come grandi contenitori composti di celle in cui in ognuna di esse è conservato 1 bit.

Lo schema di funzionamento di base per la lettura/scrittura di 1 bit sulla o dalla memoria prevede la presenza di tre tipi di bus. Un bus per gli indirizzi che ci permette di individuare la cella (o le celle) in cui andare a leggere/scrivere il dato, un bus di controllo che permette di decidere il tipo di operazione (lettura o scrittura) e un bus dei dati attraverso cui viaggiano bit che vanno letti o memorizzati.

Il bus degli inidirizzi è formato in genere da n fili dove ogni filo può trasportare un bit. In questo modo noi possiamo ottenere 2n indirizzamenti.

Ad esempio se n = 3, allora potremo indirizzare un numero massimo di 8 celle (000, 001, 010, 011,100, 110, 111).

Naturalmente possiamo arricchire la memoria associando ad ogni indirizzo un numero maggiore di bit memorizzati singolarmente in celle disposte su righe. Ad esempio immaginiamo di poter memorizzare ad ogni indirizzo una parola di 8 bit (quindi 8 celle).

In questo caso abbiamo un bus degli indirizzi sempre composto da n fili, un bus di controllo su cui viaggia il segnale R/W che ci indica il tipo di operazione (read, write) e un bus dei dati composto da 8 fili per contenere l’intera parola.

Fig. 1 - Memoria con parallelismo ad 8 bit ed indirizzamento a 16 bit

Un computer contiene tipicamente diversi tipi di memoria: RAM, ROM, cache e memorie di massa.

RAM

E’ la memoria ad accesso casuale (Random Access Memory) anche detta memoria centrale.La caratteristica della RAM è che i dati in essa salvati sono volatili cioè vengono completamente rimossi allo spegnimento del computer. La RAM, per questo motivo, ha bisogno di essere continuamente alimentata per poter essere i suoi dati disponibili. Le memorie RAM si dividono in RAM dinamiche e RAM statiche.

RAM dinamiche (DRAM)

Le DRAM (Dynamic Random Access Memory) sono caratterizzate da tempi di accesso che vanno dai 10 ai 70ns.Una memoria dinamica possiamo immaginarla come una matrice composta da una coppia di inidici (i,j) righe e colonne.

Ogni riga individua l’indirizzo della parola in memoria mentre la colonna individua la cella in cui il singolo bit della parola è salvato.

L’indirizzo che viaggia sul bus degli indirizzi, quindi, è composto da due parti: la prima parte che individua le righe e la seconda parte che individua le colonne.

Lo schema di indirizzamento è arricchito da due componenti: il decodificatore di riga che permette di risolvere l’indirizzamento della riga generando il segnale RAS (Row Address Strobe) e il decodificatore di colonna che permette di indirizzare invece le singole celle su ogni riga generando, a partire dalla seconda parte dell’indirizzo in bit, il segnale CAS (Column Address Strobe).

Ogni cella di ogni riga è collegata ad un circuito sense/write tramite 2 line di bit. Una linea collega la cella al bus dei dati e un’altra collega la cella al decodificatore di colonna.

La particolarità di questa memoria a matrice, è l'indirizzamento della memoria varrà la metà della dimensione del bus degli indirizzi (essendo l'indirizzo composto da due parti, una per l'individuazione delle righe e una delle colonne).

La caratteristica di queste RAM è che è necessario, periodicamente (ogni 2,16 ns), una operazione di rinfresco (refresh) del dato affinchè esso possa durare nel tempo.

Questo rallenta i tempi di accesso in quanto durante il refresh, non è possibile effettuare operazioni sulla memoria.

Pensare di eseguire il rinfresco su ogni cella, rende l’operazione troppo onerosa in termini di tempo.

E’ quindi preferibile effettuare il rinfresco una riga alla volta. Per questo si utilizza un buffer di supporto dove spostare il dato ogni volta prima di risalvarlo nella posizione in memoria occupata originariamente.

Anche in questo caso esistono due scelte implementative:

- effettuare il rinfresco riga per riga nello stesso frangente;

- effettuare il rinfresco di una riga per volta ma periodicamente;

Esistono diverse varianti di DRAM:

- EDRAM ( Enhanced Dynamic Random Access Memory): è una DRAM evoluta.

- EDO RAM (Extended Data Output RAM)

- SDRAM (Syncronous Dynamic Random Access Memory): la cui caratteristica principale è la capacità di operare in sincronismo con il clock del bus di sistema. Questo permette di ridurre i tempi di accesso fino a 10ns.

- moduli SIMM (Single Inline Memory Module): con interfaccia al bus di sistema costituita da 72 piedini. Tali moduli adottano DRAM e EDO RAM;

- moduli DIMM (Dual Inline Memory Module): con interfaccia al bus di sistema costituita da 168 piedini. Tali moduli adottano memorie SDRAM;

RAM Statica (SRAM)

La RAM statica è la memoria più veloce disponibile. Gli accessi sono tra i 6ns e i 25ns. Lo svantaggio è che sono costose e possono memorizzare solo ¼ dei dati che è possibile memorizzare in una DRAM. A differenza delle DRAM, però, non devono essere rinfrescate. Le SRAM vengono utilizzate per le cache che devono essere fortemente performanti.ROM

Le memoria ROM (Read Only Memory), sono memorie a sola lettura. I dati in essa contenuti sono persistenti questo vuol dire che allo spegnimento del computer non vengono rimossi.Esistono differenti tipi di ROM:

- ROM non programmabili: vengono prodotti con già inglobato il programma o I dati;

- PROM (Programmable Read Only Memory): sono memorie che è possibile programmare in un secondo momento ma solo una volta;

- EPROM (Erasable Programmable ROM): a differenza delle PROM, qui la programmazione può avvenire più di una volta ma deve essere preceduta da una cancellazione per mezzo di raggio ultravioletti;

- EEPROM (Electrica Erasable Programmable ROM): sono identiche alle precedenti ciò che cambia è la tecnica di cancellazione che in questo caso avviene tramite corrente elettrica;

Memoria cache

La memoria cache è una memoria che supporta la memoria RAM rendendo più veloce l’elaborazione del microprocessore.Le memorie cache sono collocate infatti sul chip del microprocessore e sono ad esso collegate attraverso bus di indirizzi e bus di dati privati.

L’introduzione della memoria cache è dovuta al fatto che durante le elaborazioni del microprocessore, capita spesso che dati prelevati dalla memoria RAM vengano utilizzati più di una volta dal microprocessore (località spaziale). Ad esempio le istruzioni di un programma sono eseguite in maniera sequenziale (sono rari i salti). Questo vuol dire che la probabilità che all’istruzione posta all’indirizzo i segue quella all’indirizzo i + di (con di molto piccolo), è molto alta. Inoltre in base al principio di località temporale, se una istruzione viene eseguita al tempo t con alta probabilità la stessa istruzione sarà rieseguita al tempo t + dt (con d

Ripetere letture sulla RAM più volte, può causare rallentamenti al microprocessore.

La memoria cache, essendo più veloce della RAM, viene utilizzata quindi per immagazzinare dati dalla RAM che vengono utilizzati più spesso dal microprocessore.

La memoria cache è più veloce della RAM per le seguenti ragioni

- è più vicina al microprocessore;

- essendo che i bus sono private, non c’è il rischio che quelle risorse siano utilizzate da altri dispositive;

Le cache sono memorie SRAM che come detto sono anche le più veloci disponibili attualmente.

Quando un microprocessore cerca un dato, effettua un tentativo di accesso alla memoria. Quando questo tentative ha successo, chiameremo questo tentative Hit. Diversamente sarà un Miss che determinerà la ricerca del dato ad un altro livello della memoria fino ad arrivare alla memoria RAM da cui il dato viene preso e memorizzato nella cache da cui poi l’esecuzione del microprocessore riprende.

Esistono però dei problem che una cache deve risolvere:

- Scegliere un metodo di indirizzamento: come scegliere il blocco della cache in cui copiare un dato blocco di memoria centrale (mapping);

- Scegliere un metodo di identificazione: come localizzare un dato blocco di istruzioni o dati all’interno della cache;

- Scegliere il metodo di lettura: come comportarsi quando si deve leggere una parola contenuta in un blocco della memoria cache;

- Scegliere il metodo di scrittura: cme comportarsi quado si deve scrivere una parola;

- Scegliere il metodo di sostituzione: come si sostituiscono i blocchi della cache al fine di liberare spazio per caricarne altri.

Metodo di indirizzamento

Esistono due metodi di indirizzamento:- indirizzamento diretto

- indirizzamento associativo

Il metodo di indirizzamento diretto, prevede che in ogni blocco della cache possono essere inseriti un certo numero di blocchi della memoria ram. Ad esempio nel blocco j della cache, si possono memorizzare i blocchi j MOD #blocchi_cache della memoria ram.

Fig. 3 - Indirizzamento diretto

L’idea di indirizzamento è la seguente: gli indirizzi in memoria centrale sono composti da tre parti, una etichetta che identifica un macroblocco della memoria centrale, il #blocco e la parola del blocco a cui si è interessati. Ad esempio l’indirizzo 101 (che è la parte più significativa della parola), identifica il macroblocco B e il blocco 5. Quindi B5. Questo metodo offre: alta velocità, basso costo ma numerosi conflitti di allocazione. Infatti se devo accedere a informazioni nel blocco B0 e B4 ho continui conflitti nonostante la cache sia parzialmente vuota. L’esecuzone dell’indirizzamento diretto segue questi passi:

- il microprocessore genera un indirizzo e verifica che l’etichetta dell’indirizzo corrisponda all’etichetta dei blocchi in cache;

- il microprocessore analizza i bit del campo blocco che puntano al blocco della cache;

Se invece sono diversi, allora è necessario caricare il blocco contenente la parola desiderata dalla memoria centrale.

Il metodo associativo, invece, prevede che ogni blocco della memoria centrale possa essere caricato in un qualsiasi blocco della cache. In questo modo si hanno pochi conflitti e si reduce al minimo la presenza di blocchi liberi non utilizzati nella cache. L’unico svantaggio è il costo elevato.

Questo metodo prevede una memoria associativa dove vengono memorizzate le associazioni tra le etichette dei blocchi in memoria centrale e gli indirizzi dei blocchi in cache.

Fig. 4 - Metodo associativo

L’indirizzo della memoria centrale è composto da due parti: l’etichetta che identifica il blocco e la parola che identifica quale parola all’interno del blocco. L’esecuzione è la seguente:

- il microprocessore gnera un indirizzo e viene analizzata la cache;

- I bit dell’etichetta dell’indirizzo di memoria centrale sono confrontati in modo associativo con tutti quelli della cache per vedere se il blocco è presente in cache;

Tuttavia con questo metodo viene usato lo spazio in maniera più efficiente riducendo i miss.

Analizziamo ora il problema della coerenza (cache hit e metodi di scrittura).

Quello che può succedere è che il blocco è in cache ma scrivendo la parola solo in cache la memoria centrale non è più allineata.

Per superare questo problema di coerenza, si usano due politiche differenti di scrittura della parola:

- Write-throught (immediate): ogni volta che il microprocessore scrive la parola in cache la scrive anche in memoria centrale;

- Write-back (differita): il processore scrive solo in cache e prosegue le attività; Il blocco viene marcato come modificato e in seguito (generalmente all’atto della rimozione per fare spazio) viene copiato in memoria centrale; Se quando il microprocessore deve scrivere non trova il blocco in cache, allora può adottare due politiche:

- Write-throught(immediate): il microprocessore bypassa la cache e scrive la parola solo in memoria centrale;

- Write-back (differita): il processore copia il blocco in cache e continua la sua attività. Il blocco viene marcato come modificato e viene copiato in memoria centrale successivamente;

- read-throught (immediata): il processore legge la parola non appena viene caricata in cache e riprende subito l’attività;

- read-back (differita): il processore attende che l’intero blocco sia stato caricato in cache, poi legge la parola e riprende l’attività;

- per indirizzamento diretto il blocco è fissato

- Least Recently User (LRU): si sostituisce il blocco di memoria usato meno recentemente;

- Random: scelta a caso

- FIFO: tratto il set come coda circolare, rimpiazzo il blocco in testa

- Cosa sono le memorie

- Quali sono le diverse tipologie di memorie e il loro utilizzo

- Come viene indirizzato il dato in memoria

- Quali sono le diverse tipologie di RAM (vantaggi e svantaggi)

- Quali sono le diverse tipologie di ROM

- Meccanismi che governano le memorie cache. Problemi di indirizzamento e coerenza dei dati.

- Siamo in grado di riconoscere in quali contesti sono necessarie dei tipi di memorie piuttosto che altre

- Siamo in grado di individuare la collocazione delle memorie all'interno di un computer

Se invece il blocco non è in cache, abbiamo una miss. Il microprocessore interrompe le operazioni, legge il blocco dalla memoria centrale e lo copia in cache.

Le politiche di lettura in quel caso sono sempre due:

Il problema si verifica quando il microprocessore deve caricare un blocco in cache ma non esistono più blocchi liberi.

La soluzione è la sostituzione di un blocco. Si sceglie un blocco dalla memoria cache che viene liberato a discapito del nuovo blocco che prende il suo posto. La politica usata è:

Cosa abbiamo imparato da questa lezione

| Conoscenze |

|

| Abilità |

|

| Competenze | Nessuna particolare competenza |