Didattica → Sistemi e Reti → L'Unità di controllo (CU) e di temporizzazone (CLOCK)

E’ l’unità più complessa del microprocessore. Può essere vista come una sorta di direttore di orchestra dove l’orchestra è composta dalle diverse unità del microprocessore.

Il suo scopo è quindi quello di impartire micro-ordini da inviare ad ogni unità in base al programma decodificato dall’unità di decodifica (prossima lezione). Ovviamente l’unità di controllo detta anche i tempi in quanto delle unità devono poter agire in maniera indipendente ma altre volte in contemporanea in base ad una temporizzazione ben stabilita.

La temporizzazione, e quindi la velocità di esecuzione delle istruzioni, è scandita da un periodo T del segnale generato da un oscillatore che nelle nuove generazioni è interno al microprocessore (diversamente dalle prime generazioni in cui era all’esterno).

Ogni ciclo macchina è scandito da brevissimi intervalli di tempo regolari generati dall’unità di temporizzazione detta anche clock (generatore di segnale) che genera un segnale ad intervalli regolari.

Ad ogni segnale, le componenti della CPU effettuano un’azione (fetch dell’istruzione, decodifica, etc.).

Ogni intervallo è detto ciclo di clock. Quindi ad ogni ciclo di clock viene eseguita una singola fase.

Se ne deduce che un ciclo macchina è costituito da un certo numero di cicli di clock variabile.

La potenza di un processore si misura in numero di cicli macchina al secondo che dipendono strettamente dalla frequenza di oscillazione del segnale stabilito dal clock.

Dunque l’unità di misura della frequenza sono gli Hertz (Hz). Maggiore è il valore in Hertz, maggiore è la frequenza, maggiore è il numero di ciclo di macchina al secondo.

La relazione tra frequenza e tempo è dunque:

Riducendo la durata dell’intervallo di tempo T, aumenta la frequenza.

Dunque possiamo dedurre le seguenti uguaglianze:

Chiaramente avere un segnale di clock ad alta frequenza significa avere migliori prestazioni da parte del microprocessore e di tutte le unità ad esso collegate che sfruttano il medesimo clock oppure le unità che hanno un segnale di clock generato in loco.

E’ chiaro che diverse unità per poter cooperare, devono in qualche modo sincronizzare i loro clock.

L’unità di decodifica, fornisce all’unità di controllo e di temporizzazione le informazioni necessarie per eseguire le istruzioni in passi elementari detti microistruzioni.

Ad ogni microistruzione corrispondono a sua volta una serie di micro-ordini.

Ogni microistruzione si svolge in un periodo T detto stato macchina.

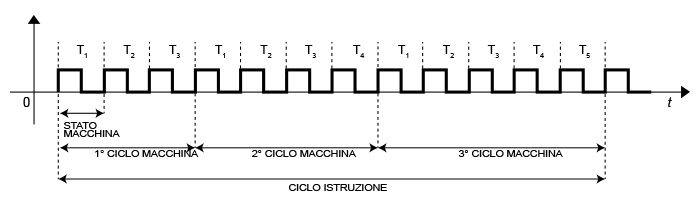

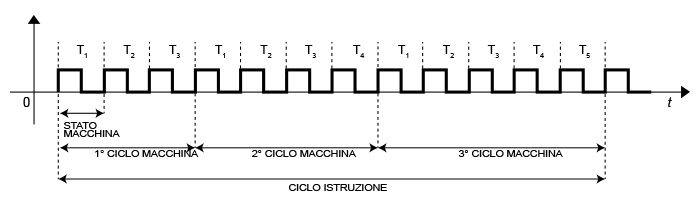

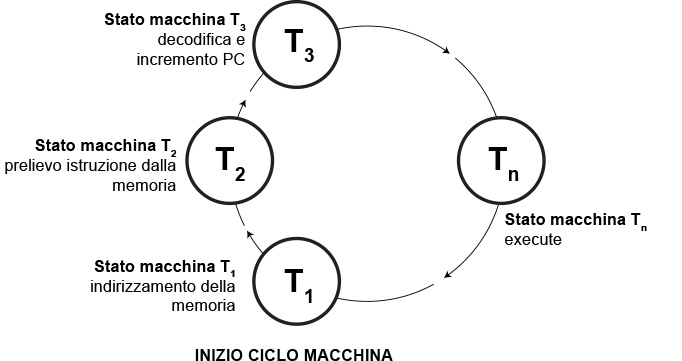

Questo vuol dire che ogni istruzione è costituita da una serie di stati macchina che costituiscono il ciclo istruzione che a sua volta è diviso in uno o più cicli macchina (Fig. 1).

Ogni ciclo macchina può essere costituito da un numero variabile di stati macchina. Il tempo di esecuzione di una istruzione è legato al numero di cicli macchina necessari per completarla.

Fig. 1 - Suddivisione del periodo di ogni ciclo istruzione in cicli macchina

Fig. 2 - Esempio di ciclo macchina

Un ciclo di istruzione, come vedremo nelle prossime lezioni, può richiedere anche più cicli macchina. L'esempio evidenzia come i primi tre stati macchina siano sempre necessari e che il numero di cicli macchina dipendano dall'istruzione specifica come vedremo nelle prossime lezioni.

Nelle esecuzione di una istruzione, come detto l'unità di controllo gioca un ruolo fondamentale in quanto dirige le varie operazioni impartendo dei micro-ordini ad ogni componente coinvolta e lo fa immettendo segnali sui bus di controllo seguento il "ritmo" imposto dal temporizzatore.

Fig. 3 - Bus di controllo

Vediamo singolarmente il significato dei singoli segnali gestiti da questa unità.

Segnali di controllo di Sistema:

Segnali di controllo della CPU:

Il microprocessore interagisce con l’esterno tramite l’unità di controllo e di temporizzazione.

Tuttavia le varie unità per poter comunicare fra di loro devono in qualche modo sincronizzarsi.

Il segnale SYNC ha durata un ciclo macchina ed è attivo quando è a livello alto.

Successivamente sempre l’unità di controllo invia verso la RAM i segnali IO/M = 0 per indicare che il dispositivo con cui vuole comunicare è proprio la RAM, e R/W = 1 per indicare una richiesta di lettura.

La RAM a sua volta risponde con un segnale di READY per comunicare al processore se è o meno disponibile alla lettura.

Se il valore di READY è 0, allora la memoria è disponibile e pronta ad effettuare la lettura. Diversamente, il microprocessore invia un segnale di WAIT = 0. Questo richiede però un ulteriore stato macchina TW in quanto il microprocessore non può procedere fino a quando la RAM non è disponibile.

Non appena la RAM invia un segnale READY = 1 (e quindi torna disponibile), il microprocessore ripristina WAIT = 1 e passa allo stato macchina T3 e i dati vengono immessi sul bus dei dati esterno concludendo il ciclo fetch.

Il meccanismo è identico nel caso di scrittura in cui la sola cosa a cambiare è il segnale di R/W che diventa 0.

Tuttavia in questo caso le periferiche possono comunicare con il microprocessore attraverso gli interrupt inviando un segnale INT = 0 nel caso in cui una periferica abbia necessità di comunicare con il microprocessore.

Quando il microprocessore riceve questo segnale pari a zero, allora invia un segnale SYNC e pone sul bus degli indirizzi l’indirizzo della periferica da cui ha ricevuto l’interrupt, attiva i segnali IO/M e R/W e se la periferica invia il segnale READY = 0 e quindi è pronta, comanda la lettura/scrittura del dato.

A differenza del caso di lettura dalla memoria in cui lo stato macchina TW è aggiunto solo quando il microprocessore è messo in attesa perchè la RAM non è pronta, nel caso di lettura scrittura su periferica lo stato macchina TW è inserito automaticamente perchè l’intervallo temporale tra l’attivazione dei segnali R/W e IO/M e l’istante di campionamento del segnale READY, risulterebbe troppo breve.

L'Unità di controllo (CU) e di temporizzazione (CLOCK)

E’ l’unità più complessa del microprocessore. Può essere vista come una sorta di direttore di orchestra dove l’orchestra è composta dalle diverse unità del microprocessore.

Il suo scopo è quindi quello di impartire micro-ordini da inviare ad ogni unità in base al programma decodificato dall’unità di decodifica (prossima lezione). Ovviamente l’unità di controllo detta anche i tempi in quanto delle unità devono poter agire in maniera indipendente ma altre volte in contemporanea in base ad una temporizzazione ben stabilita.

La temporizzazione, e quindi la velocità di esecuzione delle istruzioni, è scandita da un periodo T del segnale generato da un oscillatore che nelle nuove generazioni è interno al microprocessore (diversamente dalle prime generazioni in cui era all’esterno).

Ogni ciclo macchina è scandito da brevissimi intervalli di tempo regolari generati dall’unità di temporizzazione detta anche clock (generatore di segnale) che genera un segnale ad intervalli regolari.

Ad ogni segnale, le componenti della CPU effettuano un’azione (fetch dell’istruzione, decodifica, etc.).

Ogni intervallo è detto ciclo di clock. Quindi ad ogni ciclo di clock viene eseguita una singola fase.

Se ne deduce che un ciclo macchina è costituito da un certo numero di cicli di clock variabile.

La potenza di un processore si misura in numero di cicli macchina al secondo che dipendono strettamente dalla frequenza di oscillazione del segnale stabilito dal clock.

Dunque l’unità di misura della frequenza sono gli Hertz (Hz). Maggiore è il valore in Hertz, maggiore è la frequenza, maggiore è il numero di ciclo di macchina al secondo.

La relazione tra frequenza e tempo è dunque:

Riducendo la durata dell’intervallo di tempo T, aumenta la frequenza.

Dunque possiamo dedurre le seguenti uguaglianze:

- 1 Hz = 1 ciclo macchina al secondo

- 1 kHz = 1000 cicli macchina al secondo

- 1 MHz = 1.000.000 cicli macchina al secondo

- 1 GHz = 1.000.000.000 cicli macchina al secondo

Chiaramente avere un segnale di clock ad alta frequenza significa avere migliori prestazioni da parte del microprocessore e di tutte le unità ad esso collegate che sfruttano il medesimo clock oppure le unità che hanno un segnale di clock generato in loco.

E’ chiaro che diverse unità per poter cooperare, devono in qualche modo sincronizzare i loro clock.

L’unità di decodifica, fornisce all’unità di controllo e di temporizzazione le informazioni necessarie per eseguire le istruzioni in passi elementari detti microistruzioni.

Ad ogni microistruzione corrispondono a sua volta una serie di micro-ordini.

Ogni microistruzione si svolge in un periodo T detto stato macchina.

Questo vuol dire che ogni istruzione è costituita da una serie di stati macchina che costituiscono il ciclo istruzione che a sua volta è diviso in uno o più cicli macchina (Fig. 1).

Ogni ciclo macchina può essere costituito da un numero variabile di stati macchina. Il tempo di esecuzione di una istruzione è legato al numero di cicli macchina necessari per completarla.

Fig. 1 - Suddivisione del periodo di ogni ciclo istruzione in cicli macchina

Ciclo istruzione

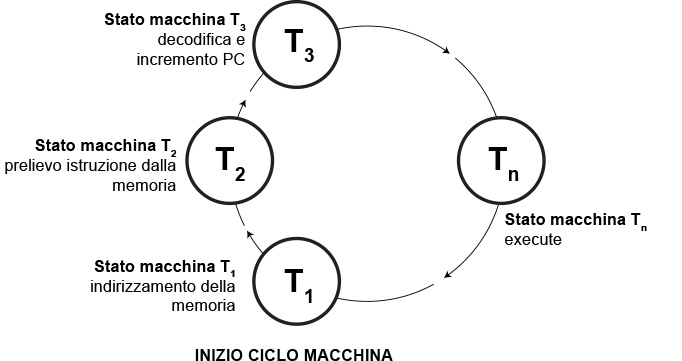

Un ciclo di istruzione (Fig. 2) è caratterizzato da due fasi fondamentali:- Ciclo di fetch: durante il quale viene prelevata dalla memoria l’istruzione che deve essere eseguita dal processore.

Il ciclo di fetch prevede almeno tre periodi T1, T2 e T3.

Durante questa fase viene immesso sul bus degli indirizzi, l’indirizzo della locazione di memoria della prossima istruzione contenuta nel PC (stato macchina T1). Viene prelevata l’istruzione dalla memoria RAM ed inserita nell’Instruction Register (stato macchina T2) per poi essere decodificata ed eseguita (stato macchina T3). L’incremento del PC può avvenire o in T2 oppure in T3 solitamente è una scelta progettuale. In qualunque dei due casi, si ha il così detto overlapping (sovrapposizione) di due microoperazioni che non si ostacolano fra di loro e che possono essere eseguite in parallelo. Generalmente il numero di stati macchina nella fase di fetch è sempre lo stesso a differenza del ciclo di execute nel quale il numero può variare in base alla complessità delle operazioni da eseguire. - Ciclo di execute: durante questo ciclo inizia l’esecuzione delle istruzioni sottoforma di micro-ordini che l’unità di controllo impartisce alle varie componenti interne ed esterne.

Fig. 2 - Esempio di ciclo macchina

Un ciclo di istruzione, come vedremo nelle prossime lezioni, può richiedere anche più cicli macchina. L'esempio evidenzia come i primi tre stati macchina siano sempre necessari e che il numero di cicli macchina dipendano dall'istruzione specifica come vedremo nelle prossime lezioni.

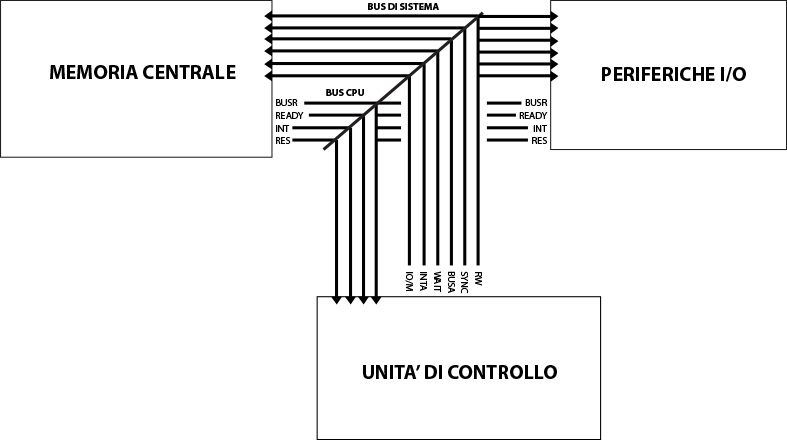

Nelle esecuzione di una istruzione, come detto l'unità di controllo gioca un ruolo fondamentale in quanto dirige le varie operazioni impartendo dei micro-ordini ad ogni componente coinvolta e lo fa immettendo segnali sui bus di controllo seguento il "ritmo" imposto dal temporizzatore.

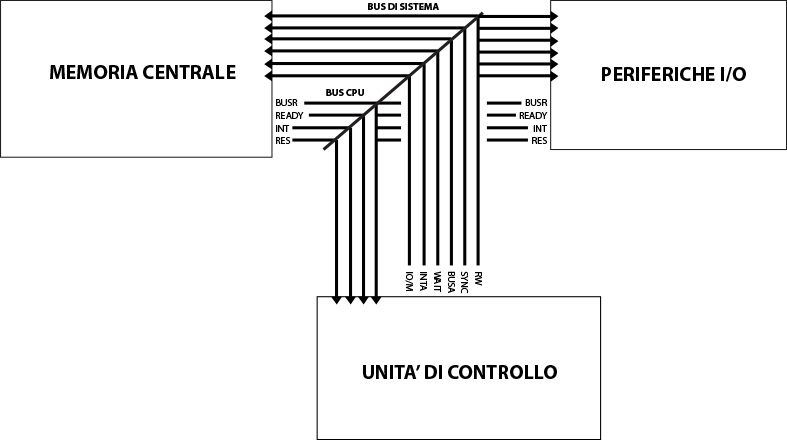

Bus di controllo

Il bus di controllo (Fig. 3) sono i bus che collegano l'unità di controllo alla CPU da e verso il mondo esterno. Essi si divide in due tipi:- Bus di sistema: Il bus di controllo del sistema è un insieme di collegamenti elettrici che consentono il transito di segnali inviati dal microprocessore all’esterno per controllare i dispositivi a cui è connesso.

- Bus della CPU: Il bus di controllo della CPU invece è un insieme di collegamenti elettrici che consentono ai dispositivi esterni di inviare segnali verso la CPU.

Fig. 3 - Bus di controllo

Vediamo singolarmente il significato dei singoli segnali gestiti da questa unità.

Segnali di controllo di Sistema:

- IO/M: è il segnale che permette al microprocessore di distinguere se rivolgere la richiesta verso una periferica o una unità di memoria. Se IO/M=1 allora si ci sta rivolgendo ad una periferica se IO/M=0 allora si ci rivolge all’unità di memoria;

- R/W: è il segnale di richiesta di lettura scrittura comunicato dal microprocessore alla periferica interessata o all’unità di memoria. Se vale 1 effettua una richiesta di lettura diversamente di scrittura;

- WAIT: è un segnale che serve al microprocessore per informare il dispositivo a cui ha fatto richiesta dell’avvenuta presa d’atto che il dispositivo non è disponibile. In tal caso WAIT=0. In questa situazione, ogni tipo di microprocessore agisce in maniera diversa. Generalmente si prevede uno stato di no operation fino a quando il segnale READY non diventa uguale a 0;

- INTA: tramite questo segnale il microprocessore risponde alla chiamata di interrupt eseguita dal dispositivo. Quando INTA = 1 allora il microprocessore rifiuta la richiesta di interrupt, se invece vale INTA = 0 la richiesta è accettata;

- SYNC: è un segnale inviato dal microprocessore verso i dispositivi esterni e serve per sincronizzare la temporizzazione dei dispositivi con quella del microprocessore;

- BUSA: è un segnale che permette al microprocessore di segnalare al dispositivo I/O la concessione dell’utilizzo dei bus per poter interagire direttamente con la memoria centrale. E’ una tecnica introdotta nelle nuove architetture detta DMA (Direct Memory Access) che porta ad ottimizzare le prestazioni. Ovviamente il segnale BUSA viene inviato in risposta al segnale di richiesta BUSR inviato dal dispositivo I/O;

Segnali di controllo della CPU:

- READY: è un segnale inviato dal dispositivo esterno per informare il microprocessore dell’eventuale disponibilità del dispositivo a rispondere ad una richiesta di lettura/scrittura. Se READY=1 il dispositivo non è pronto, diversamente se READY=0 il dispositivo è pronto;

- INT: attraverso questo segnale il dispositivo esterno invia la richiesta di interrupt al microprocessore (INT=0) diversamente INT varrà 1. A questo punto il microprocessore può accettare o meno la richiesta di interruzione utilizzando il segnale INTA;

- RES: questo segnale inviato dal dispositivo verso il microprocessore, forza il microprocessore ad azzerare il Program Counter e gli altri registri interni. In tal caso RES = 0. Se invece RES = 1 il microprocessore può seguire la normale attività;

- BUSR come anticipato è un segnale utilizzato per richiedere al processore l’accesso diretto alla memoria da parte del dispositivo I/O senza coinvolgere il microprocessore. Quando BUSR=0 la periferica richiede al microprocessore il controllo diretto del bus. In tal caso se il microprocessore risponde con BUSA=0 allora la richiesta viene accettata. Con BUSA=1 la richiesta viene rifiutata;

Temporizzazione del microprocessore

Abbiamo visto come il microprocessore interagisca con il "mondo esterno" in particolare nel caso analizzato con la memoria RAM.Il microprocessore interagisce con l’esterno tramite l’unità di controllo e di temporizzazione.

Tuttavia le varie unità per poter comunicare fra di loro devono in qualche modo sincronizzarsi.

Termporizzazione del ciclo fetch

Quando il contenuto del PC viene immesso sul bus degli indirizzi (nello stato macchina T1), contemporaneamente l’unità di controllo il segnale SYNC verso l’esterno per sincronizzare la memoria RAM esterna con la propria temporizzazione.Il segnale SYNC ha durata un ciclo macchina ed è attivo quando è a livello alto.

Successivamente sempre l’unità di controllo invia verso la RAM i segnali IO/M = 0 per indicare che il dispositivo con cui vuole comunicare è proprio la RAM, e R/W = 1 per indicare una richiesta di lettura.

La RAM a sua volta risponde con un segnale di READY per comunicare al processore se è o meno disponibile alla lettura.

Se il valore di READY è 0, allora la memoria è disponibile e pronta ad effettuare la lettura. Diversamente, il microprocessore invia un segnale di WAIT = 0. Questo richiede però un ulteriore stato macchina TW in quanto il microprocessore non può procedere fino a quando la RAM non è disponibile.

Non appena la RAM invia un segnale READY = 1 (e quindi torna disponibile), il microprocessore ripristina WAIT = 1 e passa allo stato macchina T3 e i dati vengono immessi sul bus dei dati esterno concludendo il ciclo fetch.

Il meccanismo è identico nel caso di scrittura in cui la sola cosa a cambiare è il segnale di R/W che diventa 0.

Temporizzazione in caso di lettura/scrittura da/verso le periferiche

Ovviamente il microprocessore può comunicare anche con le periferiche settando IO/M = 1 e può determinare la scrittura e la lettura dalle periferiche modificando il valore R/W uguale a 0 per la lettura e uguale a 1 per la scrittura.Tuttavia in questo caso le periferiche possono comunicare con il microprocessore attraverso gli interrupt inviando un segnale INT = 0 nel caso in cui una periferica abbia necessità di comunicare con il microprocessore.

Quando il microprocessore riceve questo segnale pari a zero, allora invia un segnale SYNC e pone sul bus degli indirizzi l’indirizzo della periferica da cui ha ricevuto l’interrupt, attiva i segnali IO/M e R/W e se la periferica invia il segnale READY = 0 e quindi è pronta, comanda la lettura/scrittura del dato.

A differenza del caso di lettura dalla memoria in cui lo stato macchina TW è aggiunto solo quando il microprocessore è messo in attesa perchè la RAM non è pronta, nel caso di lettura scrittura su periferica lo stato macchina TW è inserito automaticamente perchè l’intervallo temporale tra l’attivazione dei segnali R/W e IO/M e l’istante di campionamento del segnale READY, risulterebbe troppo breve.

Cosa abbiamo imparato da questa lezione

| Conoscenze |

|

| Abilità |

|

| Competenze |

|