Didattica → Sistemi e Reti → Il microprocessore (CPU)

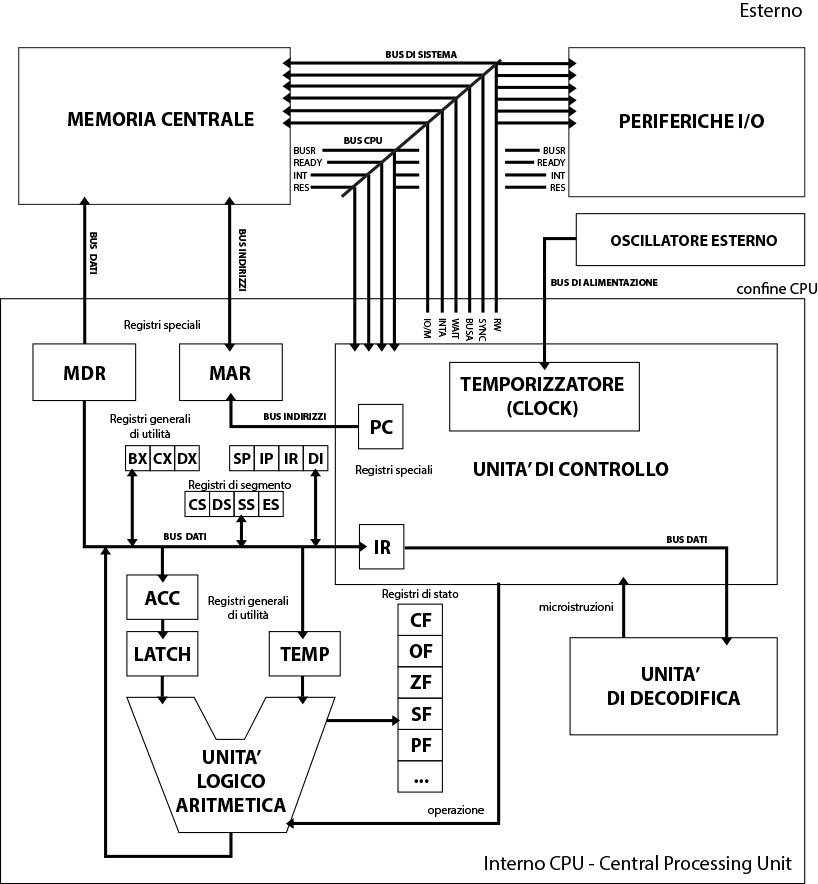

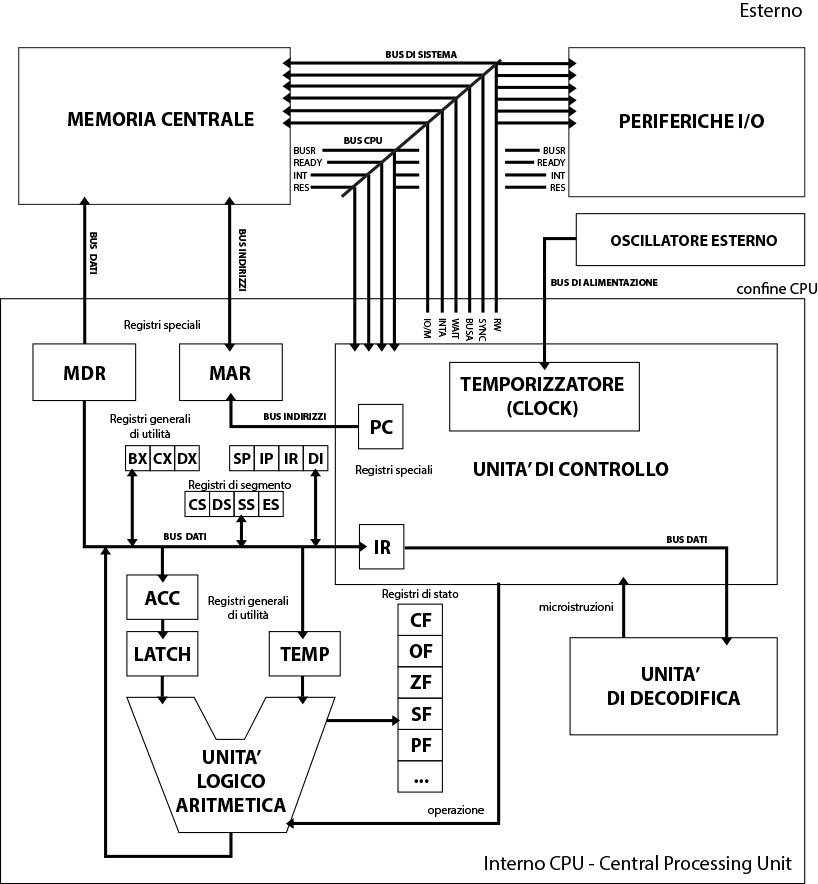

Il microprocessore o CPU (Central Processing Unit) è composto da tre parti fondamentali (Fig. 1):

Fig. 1 - Architettura di un Computer

Il funzionamento base del microprocessore prevede il prelevamento dell’istruzione che deve essere eseguita dalla memoria. Tale istruzione viene trasferita in un registro del microprocessore per poi essere codificata cioè tradotta in un insieme di segnali che “guidano” le componenti del microprocessore all’esecuzione dell’operazione specificata nella stessa istruzione.

Esso viene suddiviso nei seguenti quattro passi:

Esistono diversi tipi di bus in un microprocessore:

Dunque sui bus dei dati viaggiano i dati e le istruzioni da e verso i dispositivi.

Sui bus di indirizzo il microprocessore immette gli indirizzi di memoria (o delle periferiche) che identificano il dato da leggere o scrivere in memoria (o ingress/uscita delle periferiche). Sui bus di controllo viaggiano le informazioni ausiliarie per la definizione delle operazioni da compiere e per la sincronizzazione tra i dispositivi.

Ad esempio: lettura dalla memoria.

E’ detta anche logica di incremento/decremento (INC/DEC) perchè prevede un incremento o un decremento dell’indirizzo che punta ad una successiva o precedente cella di memoria ad esempio. Le operazioni di indirizzamento si avvalgono del bus degli indirizzi interno.

Nella logica di indirizzamento si utilizzano i seguenti registri:

Dunque tali inidirizzi hanno una parte destra ed una parte sinistra. Ad esempio il registro AX in realtà è composto da AH e da AL entrambi ad 8 bit.

Facciamo un esempio di esecuzione di una istruzione per comprendere affondo come opera il processore.

Immaginiamo di eseguire una somma tra il contenuto della cella di memoria individuata dalla parola di indirizzamento 000Ah (per specificare che un valore è in esadecimale lo si fa seguire dalla lettere h) e il contenuto del registro AL.

L’espressione nel linguaggio Assembly (il linguaggio più vicino alla macchina) è:

ADD [000Ah], AL

Supponiamo l'istruzione sia contenuta nella cella di memoria 0100h.

Questo ultimo passo (il calcolo e la memorizzazione in un registro del risultato) è detto data path. E’ importante sapere che non tutte le istruzioni sono elementari come la somma in cui è sufficiente un solo data path. Ad esempio la divisione è una istruzione più complessa da eseguire in cui sono necessari più data path per arrivare al risultato finale. Per questo motivo nella fase di execute si possono verificare più cicli di data path.

Questo procedimento appena descritto attraverso il quale la CPU esegue l’istruzione, è detto ciclo macchina.

Nel precedente esempio, sono stti necessari due cicli macchina.

Ma, come vedremo più avanti quando parleremo di cicli di clock, stato macchina e cicli di istruzione, esistono istruzioni che possono essere eseguiti in un solo ciclo macchina, oppure in cui sono necessari anche più di due cicli macchina per la loro completa esecuzione. Si noti che l’accesso ai registri avviene tramite segnali generati dall’unità di controllo e che restano all’interno del microprocessore. Questo rende l’accesso ai registri interni molto più rapido rispetto agli accessi alle unità di memoria esterne che richiedono più passaggi.

Oltre alle quattro fasi precedentemente introdotte, ne esiste una quinta detta di reset che realizza un azzeramento delle condizioni di partenza del microprocessore al termine dell’esecuzione delle istruzioni.

Il microprocessore (CPU)

Il microprocessore o CPU (Central Processing Unit) è composto da tre parti fondamentali (Fig. 1):

- ALU (Unità Artimetico-Logica): che si occupa di effettuare operazioni aritmetiche e logiche;

- CU (Unità di Controllo): che si occupa di gestire le operazioni di colloquio fra i blocchi funzionali che costituiscono il microprocessore e il mondo esterno;

- Registri: sono delle singole unità di memoria utilizzate dal microprocessore come supporto per effettuare le operazioni;

Fig. 1 - Architettura di un Computer

Il funzionamento base del microprocessore prevede il prelevamento dell’istruzione che deve essere eseguita dalla memoria. Tale istruzione viene trasferita in un registro del microprocessore per poi essere codificata cioè tradotta in un insieme di segnali che “guidano” le componenti del microprocessore all’esecuzione dell’operazione specificata nella stessa istruzione.

Esso viene suddiviso nei seguenti quattro passi:

- Fase di Fetch dell’istruzione: l’unità di controllo (CU) attiva i circuiti per la lettura di una cella di memoria il cui indirizzo è contenuto in un registro specifico, il program counter (PC). Una volta letta l’istruzione, essa viene spostata in un altro registro, l’instruction register (IR). Al termine della lettura della cella di memoria ed il trasferimento del suo contenuto nell’apposito registro, il program counter viene incrementato (punterà alla cella successiva della memoria e quindi all’istruzione successiva);

- Fase di Decode dell’istruzione: in questa fase il codice macchina dell’istruzione viene codificato, dalla Unità di decodifica, in una serie di segnali che dirigono la CPU nell’esecuzione delle operazioni. La decodifica può avvenire in due modi: o attraverso dei circuiti logici predisposti al momento della costruzione del processore oppure attraverso dei programmi interni memorizzati in maniera indelebile all’interno di una memoria speciale detta ROM (Read Only Memory) che vedremo più avanti;

- Fase di Fetch degli operandi (dati): questa fase dipende dal contenuto dell’istruzione e dalla sua codifica. Se l’operazione che si vuole eseguire richiede degli operandi, questa fase è resa necessaria. L’unità di controllo attiva I circuiti di lettura della o delle celle di memoria in cui sono presenti i dati necessari all’operazione e vengono trasferiti negli appositi registri (alcune operazioni usano come operandi valori contenuti in registri e non in memoria, in questi casi non è necessaria questa fase);

- Fase di Execute: A questo punto viene eseguita l’istruzione e il risultato viene memorizzato in un registro oppure in una qualche cella di memoria;

BUS

Tutte le componenti del microprocessore (ALU, CU, Registri, etc.) sono connesse tra di loro attraverso dei bus che non sono altro che dei fili saldati che attraversano la scheda madre.Esistono diversi tipi di bus in un microprocessore:

- Bus degli indirizzi esterno: è monodirezionale e collega il microprocessore con l’unità di memoria e con le periferiche;

- Bus degli indirizzi interno: è monodirezionale e collega il microprocessore alle componenti interne (ALU, registri di utilità, etc.);

- Bus dei dati esterno: è bidirezionale in quanto da questo bus i dati e le istruzioni viaggiano dalle unità di memoria verso il microprocessore e vicersa;

- Bus di dati interno: è bidirezionale in quanto da questo bus i dati e le istruzioni attraversano i vari blocchi;

- Bus di controllo del sistema: è monodirezionale e su cui viaggiano i segnali dal microprocessore verso i dispositivi a cui è connesso;

- Bus di controllo del microprocessore: è monodirezionale e su cui passano i segnali generati dai dispositivi esterni verso il microprocessore;

- Bus di alimentazione: costituiti dalla linea di alimentazione +Vcc , dalla massa GND e dal segnale di temporizzazione;

Dunque sui bus dei dati viaggiano i dati e le istruzioni da e verso i dispositivi.

Sui bus di indirizzo il microprocessore immette gli indirizzi di memoria (o delle periferiche) che identificano il dato da leggere o scrivere in memoria (o ingress/uscita delle periferiche). Sui bus di controllo viaggiano le informazioni ausiliarie per la definizione delle operazioni da compiere e per la sincronizzazione tra i dispositivi.

Ad esempio: lettura dalla memoria.

- La CPU fornisce l’indirizzo della parola desiderata sul bus degli indirizzi;

- Viene richiesta l’operazione di lettura attivando il bus di controllo;

- Quando la memoria ha reso disponibile la parola richiesta, il dato viene trasferito sul bus dei dati e la CPU può prelevarlo dal bus dei dati ed utilizzalo nelle sue elaborazioni;

REGISTRI

Esistono diverse tipologie di registri:- Registri speciali: sono registri non utilizzabili dal programmatore. Sono fondamentali per un corretto funzionamento del processore;

- Registri generali: sono registri che il programmatore può utilizzare per muovere dati rendendo la programmazione agevole;

Registri speciali

La logica di indirizzamento è l'operazione di indirizzamento, da parte della CPU, ai dispositivi esterni (unità di memoria e periferiche).E’ detta anche logica di incremento/decremento (INC/DEC) perchè prevede un incremento o un decremento dell’indirizzo che punta ad una successiva o precedente cella di memoria ad esempio. Le operazioni di indirizzamento si avvalgono del bus degli indirizzi interno.

Nella logica di indirizzamento si utilizzano i seguenti registri:

- PC (Program Counter): contiene l’indirizzo della locazione di memoria in cui è presente la prossima istruzione da eseguire. Più precisamente durante la fase di fetch il suo contenuto viene spostato nel MAR e viene incrementato di uno. In questo modo già durante la fase di execute, tale registro conterrà l’istruzione successive da eseguire. Nel caso di una interrupt o di un jump (come vedremo nelle prossime lezioni), il contenuto del program counter viene salvato al top dello stack in memoria (un'area specifica della memoria adibita a speciali funzioni) e al suo interno viene caricato l’indirizzo del programma di interrupt oppure l’indirizzo della procedura da eseguire. Non appena la subroutine viene eseguita, il program counter riassume il valore precedente prelevandolo dallo stack;

- MAR (Memory Address Register): contiene l’indirizzo della locazione di memoria dell’istruzione attuamente in fase di esecuzione durante la fase di fetch. Durante, invece, la fase di execute, in caso di istruzione con riferimento in memoria, tale registro conterrà l’indirizzo in memoria dell’operando;

- MDR (Memory Data Register): da questo registro passano tutti i dati che sono scambiati con la memoria esterna prima di venire distribuiti negli altri registri interni;

- IR (Instruction Register): contiene la parte di codice operativo di una istruzione e quindi la sequenza di bit che determinerà l’azione del microprocessore;

- SP (Stack Pointer): contiene un puntatore all'area di memoria contenente il contesto dell'istruzione precedentemente interrotta;

- CS (Code Segment): contiene l’indirizzo della locazione di memoria in cui è presente la prossima istruzione da eseguire. Più precisamente durante la fase di fetch il suo contenuto viene spostato nel MAR e viene incrementato di uno. In questo modo già durante la fase di execute, tale registro conterrà l’istruzione successive da eseguire. Nel caso di una interrupt o di un jump, il contenuto del program counter viene salvato al top dello stack in memoria e al suo interno viene caricato l’indirizzo del programma di interrupt oppure l’indirizzo della procedura da eseguire. Non appena la subroutine viene eseguita, il program counter riassume il valore precedente prelevandolo dallo stack;

- DS (Data Segment): contiene l’indirizzo della locazione di memoria dell’istruzione attuamente in fase di esecuzione durante la fase di fetch. Durante, invece, la fase di execute, in caso di istruzione con riferimento in memoria, tale registro conterrà l’indirizzo in memoria dell’operando;

- ES (Extra Segment): da questo registro passano tutti i dati che sono scambiati con la memoria esterna prima di venire distribuiti negli altri registri interni;

- SS (Stack Segment): contiene la parte di codice operativo di una istruzione e quindi la sequenza di bit che determinerà l’azione del microprocessore;

- CARRY (CF o C, cioè bit di riporto): conterrà 1 se l’operazione effettuata è una somma e un bit è di riporto, oppure se l’operazione è di sottrazione e c’è un prestito. 0 diversamente;

- OVERFLOW (OF o W): sarà pari a 1 quando una operazione aritmetica restituisce un risultato non rappresentabile con il parallelismo del microprocessore. Ad esempio se il parallelismo è di 8 bit, allora potremo rappresentare solo i numeri che vanno da -128 a +127. Diversamente è settato a 0;

- PARITA’ (PF o P): sarà pari a 1 quando una operazione logica dà un numero di bit pari. Dirversamente sarà pari a 0;

- ZERO (ZF o Z): è settato ad 1 se il risultato dell’operazione restituisce 0. Diversamente varrà 0;

- SIGN (SF o N, numero negativo): è settato ad 1 se il risultato dell’operazione è un numero negativo (il bit più significativo è pari ad 1). Diversamente è pari a 0;

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OF | SF | ZF | PF | CF |

Registri generali

E' l'insieme di tutti i registri che il programmatore può utilizzare per rendere agevole la programmazione.- AX (Accumulatore) o ACC

- BX (Base)

- CX (Contatore)

- DX (Data)

- TEMP (Temporaneo)

- LATCH ACC

Dunque tali inidirizzi hanno una parte destra ed una parte sinistra. Ad esempio il registro AX in realtà è composto da AH e da AL entrambi ad 8 bit.

| 15 | 0 |

| AX | |

| AH | AL |

Facciamo un esempio di esecuzione di una istruzione per comprendere affondo come opera il processore.

Immaginiamo di eseguire una somma tra il contenuto della cella di memoria individuata dalla parola di indirizzamento 000Ah (per specificare che un valore è in esadecimale lo si fa seguire dalla lettere h) e il contenuto del registro AL.

L’espressione nel linguaggio Assembly (il linguaggio più vicino alla macchina) è:

Supponiamo l'istruzione sia contenuta nella cella di memoria 0100h.

- Fetch dell’istruzione: viene prelevato il contenuto del PC che ha come valore 0100h. Questo valore viene trasferito, attraverso il bus degli indirizzi interno, nel registro MAR. Da questo registro avviene un indirizzamento alla cella 0100h attaverso il bus degli indirizzi esterno e il suo contenuto viene trasferito prima nel registro MDR attraverso il bus dei dati esterno e successivamente nel registro IR attarverso il bus dei dati interno. IR, ora, contiene la sequenza binaria dell'istruzione che si vuole eseguire;

- Decode: viene decodificata la sequenza binaria contenuta nel registro IR come operazione di somma (ADD). Vengono predisposti i circuiti per effettuare una somma;

- Fetch degli operandi: dall’istruzione decodificata, la CPU evince che un operando deve essere recuperato dalla memoria esattamente nella cella 000Ah. Dunque avviene un altro indirizzamento: l'indirizzo 000Ah viene spostato nel MAR dopodichè dalla memoria viene prelevato il suo contenuto e spostato nel registro MDR. Dal registro MDR il dato viene trasferito in uno dei registri di general purpose di utilità;

- Execute: il contenuto della cella di memoria 000Ah prelevato nella precedente fase è ora disponibile in un registro di utilità, dunque viene sommato al contenuto del registro AL. Il risultato della somma viene spostato in un altro registro;

Questo ultimo passo (il calcolo e la memorizzazione in un registro del risultato) è detto data path. E’ importante sapere che non tutte le istruzioni sono elementari come la somma in cui è sufficiente un solo data path. Ad esempio la divisione è una istruzione più complessa da eseguire in cui sono necessari più data path per arrivare al risultato finale. Per questo motivo nella fase di execute si possono verificare più cicli di data path.

Questo procedimento appena descritto attraverso il quale la CPU esegue l’istruzione, è detto ciclo macchina.

Nel precedente esempio, sono stti necessari due cicli macchina.

Ma, come vedremo più avanti quando parleremo di cicli di clock, stato macchina e cicli di istruzione, esistono istruzioni che possono essere eseguiti in un solo ciclo macchina, oppure in cui sono necessari anche più di due cicli macchina per la loro completa esecuzione. Si noti che l’accesso ai registri avviene tramite segnali generati dall’unità di controllo e che restano all’interno del microprocessore. Questo rende l’accesso ai registri interni molto più rapido rispetto agli accessi alle unità di memoria esterne che richiedono più passaggi.

Oltre alle quattro fasi precedentemente introdotte, ne esiste una quinta detta di reset che realizza un azzeramento delle condizioni di partenza del microprocessore al termine dell’esecuzione delle istruzioni.

Cosa abbiamo imparato da questa lezione

| Conoscenze |

|

| Abilità |

|

| Competenze | Nessuna particolare competenza |